# N717-EA Hardware User Guide

LTE Cat.1 Issue 1.0 Date 2023-11-06

#### Copyright © Neoway Technology Co., Ltd 2022. All rights reserved.

No part of this document may be reproduced or transmitted in any form or by any means without prior written consent of Neoway Technology Co., Ltd.

**NEOWOY** is the trademark of Neoway Technology Co., Ltd.

All other trademarks and trade names mentioned in this document are the property of their respective holders.

#### **Notice**

This document provides guide for users to use N717-EA.

This document is intended for system engineers (SEs), development engineers, and test engineers.

THIS GUIDE PROVIDES INSTRUCTIONS FOR CUSTOMERS TO DESIGN THEIR APPLICATIONS. PLEASE FOLLOW THE RULES AND PARAMETERS IN THIS GUIDE TO DESIGN AND COMMISSION. NEOWAY WILL NOT TAKE ANY RESPONSIBILITY OF BODILY HURT OR ASSET LOSS CAUSED BY IMPROPER OPERATIONS.

THE INFORMATION IN THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE DUE TO PRODUCT VERSION UPDATE OR OTHER REASONS.

EVERY EFFORT HAS BEEN MADE IN PREPARATION OF THIS DOCUMENT TO ENSURE ACCURACY OF THE CONTENTS, BUT ALL STATEMENTS, INFORMATION, AND RECOMMENDATIONS IN THIS DOCUMENT DO NOT CONSTITUTE A WARRANTY OF ANY KIND, EXPRESS OR IMPLIED.

Neoway provides customers with complete technical support. If you have any question, please contact your account manager or email to the following email addresses:

Sales@neoway.com

Support@neoway.com

Website: http://www.neoway.com

# Contents

| 1 About N717-EA                              | 10 |

|----------------------------------------------|----|

| 1.1 Product Overview                         | 10 |

| 1.2 Block Diagram                            | 10 |

| 1.3 Basic Features                           |    |

| 2 Reference Standard                         | 14 |

| 3 Pin Definitions                            |    |

| 3.1 Pad Layout                               | 15 |

| 3.2 Pin Description                          |    |

| 4 Application Interfaces                     |    |

| 4.1 Power Interfaces                         | 21 |

| 4.1.1 VBAT                                   |    |

| 4.1.2 VDD 1P8                                | 26 |

| 4.2 Control Interfaces                       | 26 |

| 4.2.1 Module Power-on                        | 27 |

| 4.2.2 Module Power-off                       | 29 |

| 4.2.3 Module Reset                           | 31 |

| 4.3 Peripheral Interfaces                    | 32 |

| 4.3.1 USB                                    | 33 |

| 4.3.2 UART                                   | 34 |

| 4.3.3 USIM                                   | 37 |

| 4.3.4 PCM                                    | 40 |

| 4.3.5 I2C                                    | 41 |

| 4.4 Audio Interfaces                         | 42 |

| 4.4.1 Analog Audio Input                     | 42 |

| 4.4.2 Analog Audio Output                    | 44 |

| 4.5 RF Interface                             | 45 |

| 4.5.1 ANT_MAIN Antenna Interface             | 45 |

| 4.5.2 Antenna Assembling                     |    |

| 4.6 Other Functional Interfaces              | 50 |

| 4.6.1 WAKEUP_IN                              | 50 |

| 4.6.2 Network Status Indication              | 52 |

| 4.6.3 USB_BOOT                               | 53 |

| 5 Electrical Characteristics and Reliability | 54 |

| 5.1 Electrical Characteristics               | 54 |

| 5.2 Temperature Characteristics              | 55 |

| 5.3 ESD Protection Characteristics           | 55 |

| 6 RF Characteristics                         | 56 |

| 6.1 Operating Frequency Bands                | 56 |

| 6.2 Power and Sensitivity                    | 56 |

|                                              |    |

| 7 Mechanical Characteristics     | 59 |

|----------------------------------|----|

| 7.1 Dimensions                   | 59 |

| 7.2 Labeling                     | 60 |

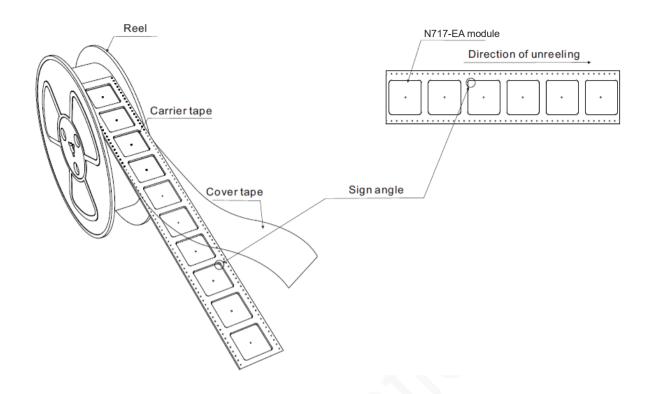

| 7.3 Packaging                    |    |

| 7.3.1 Reels                      | 60 |

| 7.3.2 Moisture                   | 61 |

| 8 Mounting                       | 62 |

| 8.1 PCB Package                  | 62 |

| 8.2 Application PCB Package      | 63 |

| 8.3 Stencil                      |    |

| 8.4 Solder Paste                 | 64 |

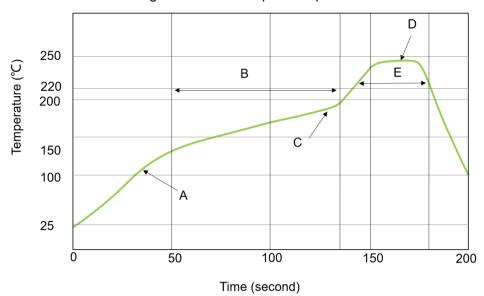

| 8.5 SMT Oven Temperature Profile | 64 |

| A Abbreviations                  | 66 |

# Table of Figures

| Figure 1-1 Block diagram                                                        | 11 |

|---------------------------------------------------------------------------------|----|

| Figure 3-1 N717-EA pad layout (top view)                                        | 15 |

| Figure 4-1 Voltage drops of the power supply.                                   | 22 |

| Figure 4-2 Recommended power supply design 1                                    | 23 |

| Figure 4-3 Recommended power supply design 2                                    | 23 |

| Figure 4-4 Recommended power supply design3                                     | 24 |

| Figure 4-5 Recommended power supply design4                                     |    |

| Figure 4-6 Reference design of key-control startup                              |    |

| Figure 4-7 Reference design of MCU-control startup                              |    |

| Figure 4-8 Power-on process                                                     | 29 |

| Figure 4-9 Reference design of automatic startup once powered up                | 29 |

| Figure 4-10 N717-EA hardware power-off process                                  | 30 |

| Figure 4-11 Key-control reset                                                   | 31 |

| Figure 4-12 MCU-control reset                                                   | 32 |

| Figure 4-13 Module reset process                                                | 32 |

| Figure 4-14 Recommended design of the USB interface                             | 33 |

| Figure 4-15 Reference design of the UART interface                              | 34 |

| Figure 4-16 Recommended voltage-level translation circuit 1                     | 35 |

| Figure 4-17 Recommended voltage-level translation circuit 2                     | 36 |

| Figure 4-18 Recommended voltage-level translation circuit 3                     | 37 |

| Figure 4-19 Recommended design of the USIM interface (normally close connector) | 38 |

| Figure 4-20 Recommended design of the USIM interface (normally open connector)  | 39 |

| Figure 4-21 Reference design of USIM card interface (without hot swap function) | 40 |

| Figure 4-22 Reference design of the PCM interface                               | 41 |

| Figure 4-23 Reference design of the I2C interface                               | 42 |

| Figure 4-24 Reference design of the differential MIC input                      | 43 |

| Figure 4-25 Reference design of the differential SPK input                      | 44 |

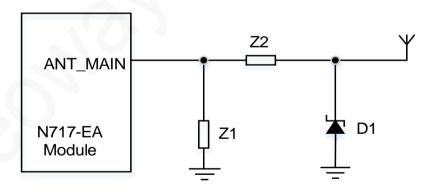

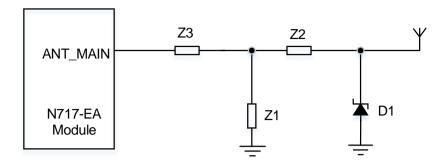

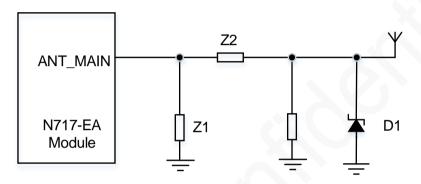

| Figure 4-26 L-type RF matching schematics                       | 45 |

|-----------------------------------------------------------------|----|

| Figure 4-27 T-type RF matching schematics                       | 46 |

| Figure 4-28 π-type RF matching schematics                       | 46 |

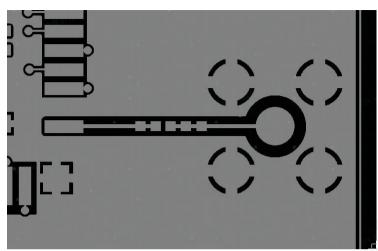

| Figure 4-29 Recommended RF PCB design                           | 47 |

| Figure 4-30 Murata RF connector encapsulation specifications    | 48 |

| Figure 4-31 RF cable connections                                | 48 |

| Figure 4-32 Antenna layout                                      | 49 |

| Figure 4-33 Clearance area around the antenna on the PCB board  | 49 |

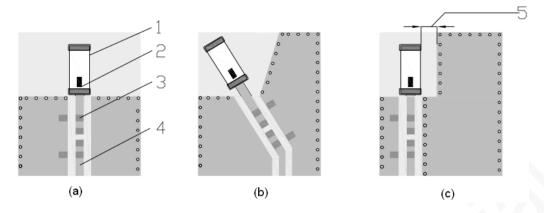

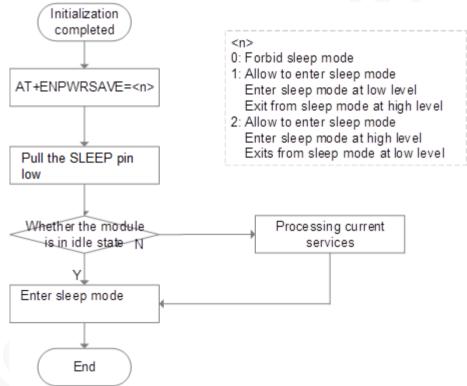

| Figure 4-34 Process of entering into sleep mode                 | 50 |

| Figure 4-35 Process of processing data services in sleep mode   | 51 |

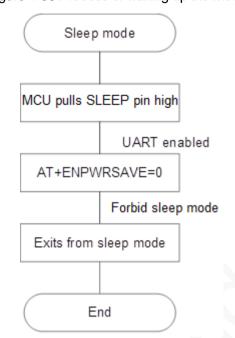

| Figure 4-36 Process of waking up the module                     | 52 |

| Figure 4-37 Driving LED indicators with a triode                | 53 |

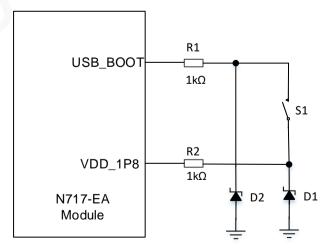

| Figure 4-38 Reference design of USB_BOOT pin                    | 53 |

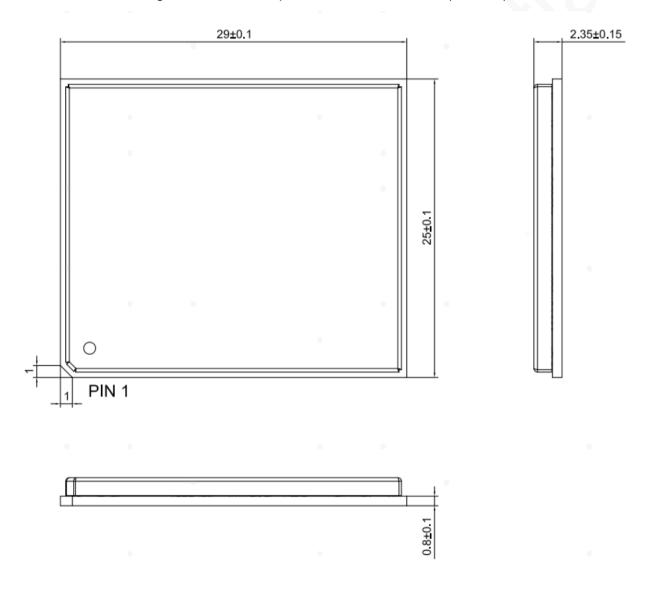

| Figure 7-1 N717-EA top and side view dimensions (unit: mm)      | 59 |

| Figure 8-1 N717-EA PCB package (bottom view, unit: mm)          | 62 |

| Figure 8-2 N717-EA application PCB package (top view, unit: mm) | 63 |

| Figure 8-3 Oven temperature profile                             | 65 |

# Table of Tables

| Table 1-1 Models and frequency bands             | 10 |

|--------------------------------------------------|----|

| Table 3-1 IO types and DC characteristics        | 16 |

| Table 3-2 Pin definitions                        | 17 |

| Table 4-1 Power-on description                   | 27 |

| Table 5-1 N717-EA electrical characteristics     | 54 |

| Table 5-2 N717-EA current consumption (typical)  | 54 |

| Table 5-3 N717-EA temperature characteristics    | 55 |

| Table 5-4 N717-EA ESD protection characteristics | 55 |

| Table 6-1 N717-EA operating frequency bands      | 56 |

| Table 6-2 N717-EA RF transmitting power          | 56 |

| Table 6-3 N717-EA GSM RX sensitivity             | 57 |

| Table 6-4 N717-EA LTE RX sensitivity             | 57 |

# **About This Document**

# Scope

This document is applicable to N717-EA.

It defines the features, indicators, and test standards of the N717-EA module and provides reference for the hardware design of each interface.

## **Audience**

This document is intended for system engineers (SEs), development engineers, and test engineers.

# **Change History**

| Issue | Date    | Change        | Changed By   |

|-------|---------|---------------|--------------|

| 1.0   | 2022-12 | Initial draft | Wu Yongqiang |

## Conventions

| Symbol | Indication                                                                                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------|

| 0      | This warning symbol means danger. You are in a situation that could cause fatal device damage or even bodily damage.    |

| !      | Means reader be careful. In this situation, you might perform an action that could result in module or product damages. |

| •      | Means note or tips for readers to use the module                                                                        |

## **Related Documents**

Neoway\_N717-EA\_Datasheet

Neoway\_N717-EA\_Product\_Specifications

Neoway\_N717\_AT\_Command\_Mannual

Neoway\_N717-EA\_EVK\_User\_Guide

## 1 About N717-EA

This chapter introduces the product overview, block diagram, and basic features of N717-EA.

## 1.1 Product Overview

N717-EA is an LTE industrial-grade cellular modules with dimensions of  $(29.0 \pm 0.10)$  mm ×  $(25.0 \pm 0.10)$  mm ×  $(2.35 \pm 0.15)$  mm. It provides with dimensions of on GSM, FDD-LTE (Cat 1) and TDD-LTE (Cat 1) networks, especially on B31 (450 MHz). It provides various hardware interfaces and is suitable for developing IoT communications devices such as wireless meter reading terminal and industrial router that are widely used in power and industrial markets.

N717-EA has the following features:

- ARM Cortex-R5 processor, 614 MHz CPU clock speed, 32 KB L1 cache

- Available networks: GSM/GPRS & LTE Cat 1

- Supported interfaces: USB2.0/USIM/UART/PCM/I2C/MIC/SPK

Table 1-1 lists variants and frequency bands that N717-EA supports.

Table 1-1 Models and frequency bands

| Model | Region | Category | Frequency band                                                                            |

|-------|--------|----------|-------------------------------------------------------------------------------------------|

| EA    | Europe | Cat1     | FDD-LTE: B1, B3, B5, B7, B8, B20, B28, B31<br>TDD-LTE: B38, B40, B41<br>GSM: 900/1800 MHz |

# 1.2 Block Diagram

N717-EA includes the following functional units:

- Baseband chip

- 26 MHz crystal

- Power management

- RF functional

- Digital interfaces (USIM, I2C, UART, USB, and PCM)

- Analog interfaces (MIC, SPK)

ANT\_MAIN VBAT\_RF RF Front-End RF transceiver PWR\_n VBAT\_BB Baseband Power 26 MHz PWRKEY\_N Control manager crystal QSPI flash (8 MB) + pSRAM (16 MB) I2C RESET\_N Interface USIM MIC SPK I2C PCM UART USB РС

Figure 1-1 Block diagram

## 1.3 Basic Features

| Features           | Description                                                                                                                                        |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Physical features  | <ul> <li>Dimensions: (29.0 ± 0.10) mm × (25.0 ± 0.10) mm × (2.35 ± 0.15) mm</li> <li>Package: LGA (126 pads)</li> <li>Weight: about TBD</li> </ul> |  |

| Temperature ranges | <ul> <li>Operating: -30°C to +75°C</li> <li>Extended: -40°C to +85°C</li> <li>Operating: -40°C to +90°C</li> </ul>                                 |  |

| Operating voltage (DC) | VBAT: 3.4 V to 4.2 V, typical value: 3.6 V                                                                                                                                                              |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Sleep mode <sup>1</sup> : TBD                                                                                                                                                                           |

| Operating current (DC) | <sup>2</sup> : TBD                                                                                                                                                                                      |

|                        | Operating mode <sup>3</sup> (LTE system): TBD                                                                                                                                                           |

| Embedded processor     | ARM Cortex-R5 processor, 614 MHz CPU clock speed, 32 KB L1 cache                                                                                                                                        |

| Memory                 | RAM: 16 MB<br>ROM: 8 MB                                                                                                                                                                                 |

| Frequency band         | See Table 1-1.                                                                                                                                                                                          |

| Wireless rate          | GPRS: Max 85.6 Kbps (DL)/Max 85.6 Kbps (UL) EDGE: Max 236.8 Kbps(DL)/Max 236.8 Kbps(UL) FDD-LTE: Cat1, Max 10 Mbps (DL)/Max 5 Mbps (UL) TDD-LTE: Cat1, Max 8 Mbps (DL)/Max 2 Mbps (UL)                  |

| Transmit power         | EGSM900: 33 dBm ±2 dB (Power Class 4) DCS1800: 30 dBm ±2 dB (Power Class 1) EGSM900 8-PSK: 27 dBm ±3 dB (Power Class E2) DCS1800 8-PSK: 26 dBm ±3 dB (Power Class E2) LTE: 23 dBm ±2 dB (Power Class 3) |

|                        | 2G/4G antenna, with a characteristic impedance of 50 $\Omega$ .                                                                                                                                         |

|                        | Two UART interfaces, one of which for debug.  Default baud rate: 115200 bps                                                                                                                             |

|                        | Two USIM interfaces, either 1.8 V or 3.0 V USIM card is supported. (Currently USIM2 is not supported.)                                                                                                  |

| Application Interfaces | One USB 2.0 interface, for slave mode only.                                                                                                                                                             |

| Application Interfaces | One PCM interface                                                                                                                                                                                       |

|                        | One I2C interface, for master mode only.                                                                                                                                                                |

|                        | One MIC interface                                                                                                                                                                                       |

|                        | One SPK interface, supports driving power of up to 37 mW with a 32 $\Omega$ load. If higher driving power is required, connect this interface to an external power amplifier.                           |

<sup>&</sup>lt;sup>1</sup> means the current drawn by the module in sleep mode, a low power consumption state, in which its RF function is functioning properly but its peripheral interfaces are disabled. If there is an incoming call or SMS, the module will exit from the sleep mode, and after the incoming call or voice instant messaging has ended, the module will re-enter the sleep mode.

<sup>&</sup>lt;sup>2</sup> means the current drawn by the module in a normal operating mode, but no data service is being processed.

<sup>&</sup>lt;sup>3</sup> means the current drawn by the module when there are on-going data services. In the operating mode, only the current value on LTE network is exemplified. For other current values on other network modes, please refer to the current test report.

| SD card AT bus         | 3GPP Release 9 Neoway extended AT commands |

|------------------------|--------------------------------------------|

| SMS                    | PDU, TXT                                   |

| Data                   | PPP                                        |

| Protocol               | TCP, UDP, FTP/FTPS                         |

| Certification approval | RoHS*, CE*                                 |

<sup>\*</sup> means under development.

## 2 Reference Standard

N717-EA is designed by referring to the following standards:

- 3GPP TS 36.521-1 V9.10.0 User Equipment (UE) conformance specification; Radio transmission and reception; Part 3: Radio Resource Management (RRM) conformance testing

- 3GPP TS 21.111 V9.0.0 USIM and IC card requirements

- 3GPP TS 31.102 V9.10.0 Characteristics of the Universal Subscriber Identity Module (USIM) application

- 3GPP TS 31.111 V9.11.0 Universal Subscriber Identity Module (USIM) Application Toolkit (USAT)

- 3GPP TS 27.007 V9.4.0 AT command set for User Equipment (UE)

- 3GPP TS 27.005 V9.0.0 Use of Data Terminal Equipment Data Circuit terminating Equipment (DTE-DCE) interface for Short Message Service (SMS) and Cell Broadcast Service (CBS)

## 3 Pin Definitions

N717-EA is equipped with 126 pads, which are introduced in LGA package. Available functional interfaces include: power supply, USB, UART, USIM, PCM, I2C, etc.

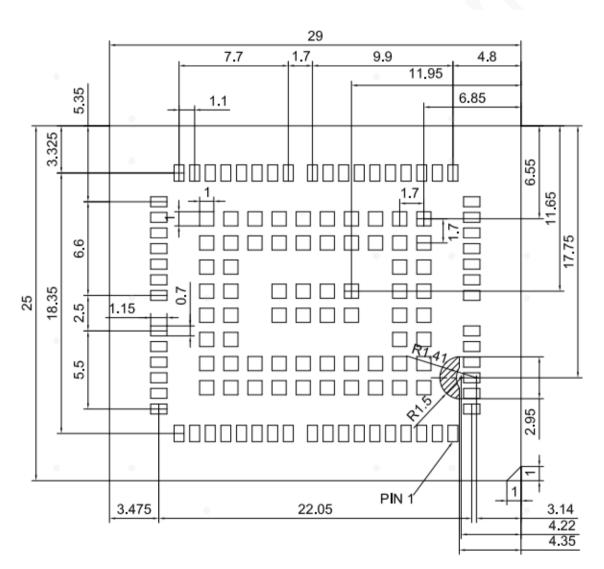

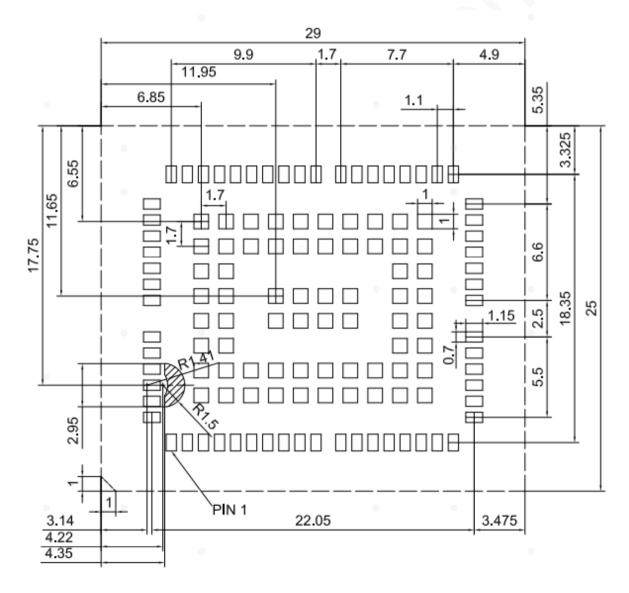

## 3.1 Pad Layout

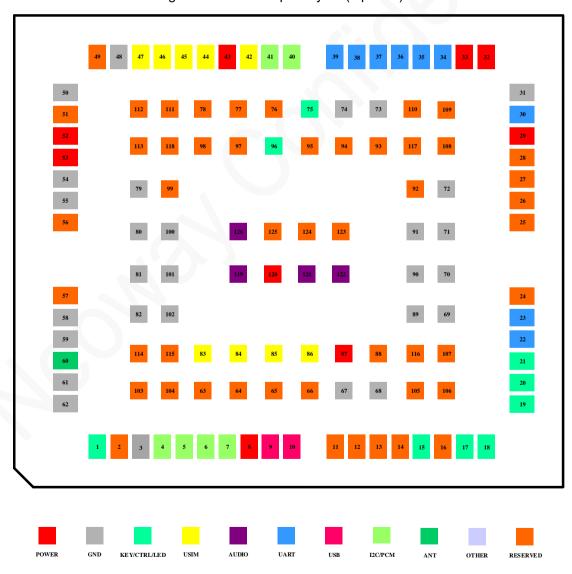

The following figure shows the pad layout of N717-EA.

Figure 3-1 N717-EA pad layout (top view)

# 3.2 Pin Description

The following table lists the IO types and DC characteristics.

Table 3-1 IO types and DC characteristics

| IO type           |                                                  |                                          |                                 |  |

|-------------------|--------------------------------------------------|------------------------------------------|---------------------------------|--|

| В                 | Digital input and output, CMOS logic level       |                                          |                                 |  |

| DO                | Digital output, CMOS logic level                 |                                          |                                 |  |

| DI                | Digital input, CMOS logic level                  |                                          |                                 |  |

| РО                | Power output                                     |                                          |                                 |  |

| PI                | Power input                                      |                                          |                                 |  |

| AO                | Analog output                                    |                                          |                                 |  |

| Al                | Analog input                                     |                                          |                                 |  |

| AIO               | Analog input and output                          |                                          |                                 |  |

| DC characte       | eristics                                         |                                          |                                 |  |

| Interface<br>type | Power domain                                     | Logic level characteristics              |                                 |  |

|                   |                                                  | 1.8 V DC characteristics                 | 3.0 V DC characteristics        |  |

|                   |                                                  | $V_{IH}=0.65V_{DD\_P1}\sim1.98V$         | $V_{IH}=2V\sim V_{DD\_P1}+0.3V$ |  |

| USIM              | P1: Either 1.8 V or 3.0 V USIM card is supported | $V_{IL}$ =-0.3 $V$ ~0.35 $V_{DD_{\_}P1}$ | $V_{IL}$ =-0.3 $V$ ~0.8 $V$     |  |

|                   |                                                  | $V_{OH}$ =1.35 $V$ ~ $V_{DD\_P1}$        | $V_{OH}=2.4V \sim V_{DD\_P1}$   |  |

|                   |                                                  | V <sub>OL</sub> =0V~0.45V                | $V_{OL}=0V\sim0.4V$             |  |

| RESET_N           | P2: 1.6V                                         | V <sub>ILmax</sub> =0.5V                 |                                 |  |

| GPIO P3: 1.8V | $V_{IH}=0.65V_{DD_P3}\sim1.98V$ $V_{IL}=-0.3V\sim0.35V_{DD_P3}$ $V_{OH}=1.35V\sim V_{DD_P3}$ $V_{OL}=0V\sim0.45V$ |

|---------------|-------------------------------------------------------------------------------------------------------------------|

|---------------|-------------------------------------------------------------------------------------------------------------------|

Table 3-2 Pin definitions

| Signal             | Pin SN    | I/O type     | Function description                  | DC characteristics/<br>power domain                 | Remarks                                                                                         |

|--------------------|-----------|--------------|---------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Power interfaces   |           |              |                                       |                                                     |                                                                                                 |

| VBAT_BB            | 32, 33    | PI           | Module baseband supply input          | $V_{min}$ =3.4V, $V_{norm}$ =3.6V,                  | The external power supply must ensure at least 0.8 A current for VBAT_BB.                       |

| VBAT_RF            | 52, 53    | PI           | RF supply input                       | V <sub>max</sub> =4.2V F supply input               |                                                                                                 |

| VDD_1P8            | 29        | PO           | 1.8 V power output                    | V <sub>norm</sub> = 1.8 V, I <sub>max</sub> = 50 mA | Only used for voltage-level translation.<br>Leave this pin open if unused.                      |

| GND                | 3, 31, 47 | - 48, 50, 54 | - 55, 58 - 59, 61- 62, 67- 74, 79 - 8 | 32, 89 - 91, 100 - 102                              | Make sure all GND pins are grounded.                                                            |

| Control interfaces |           |              |                                       |                                                     |                                                                                                 |

| PWRKEY_N           | 15        | DI           | Module on/off control                 | VBAT_BB power domain                                | A low-voltage level for a valid time period can trigger on/off of the module (see section 4.2). |

| RESET_N            | 17        | DI           | Module reset input                    | P2                                                  | Active low                                                                                      |

| WAKEUP_IN*         | 96        | DI           | Wake up the module.                   | P3                                                  | For details, see section 4.6.1.                                                                 |

| Network status indic | ation int | erface |                              |                                              |                                                                                    |  |

|----------------------|-----------|--------|------------------------------|----------------------------------------------|------------------------------------------------------------------------------------|--|

| STATUS               | 20        | DO     | Working status indication    | P3                                           | -                                                                                  |  |

| NET_LIGHT            | 21        | DO     | Network status indicator     | P3                                           | -                                                                                  |  |

| SLEEP_IND            | 1         | DO     | Sleep mode indicator         | P3                                           |                                                                                    |  |

| UART1 interface      |           |        |                              |                                              |                                                                                    |  |

| UART_DTR             | 30        | DI     | Data terminal ready          | P3                                           | ·                                                                                  |  |

| UART_RXD             | 34        | DI     | UART data input              | P3                                           |                                                                                    |  |

| UART_TXD             | 35        | DO     | UART data output             | P3                                           | <ul> <li>Software version (Standard): For<br/>communication based on AT</li> </ul> |  |

| UART_RTS             |           |        | UART ready to send           | P3                                           | commands.                                                                          |  |

| UART_CTS             |           |        | UART clear to send           | P3                                           | Software version (Open): For data transmission.                                    |  |

| ART_DCD 38 DO        |           | DO     | Data carrier detect P3       |                                              | transmission.                                                                      |  |

| UART_RI              | 39        | DO     | Ring indication              | P3                                           |                                                                                    |  |

| DEBUG UART interfa   | ice       |        |                              |                                              |                                                                                    |  |

| DEBUG_UART_RXD       | 22        | DI     | Debug UART data input        | P3                                           | - For module debugging only.                                                       |  |

| DEBUG_UART_TXD       | 23        | DO     | DEBUG UART data out          | DEBUG UART data out P3                       |                                                                                    |  |

| USIM interfaces      |           |        |                              |                                              |                                                                                    |  |

| USIM1_DET            | 42        | DI     | USIM1 hot-swapping detection | P3                                           | -                                                                                  |  |

| USIM1_VCC            | 43        | РО     | USIM1 power output           | Either 1.8 V or 3.0 V USIM card is supported | -                                                                                  |  |

| USIM1_RESET          | 44        | DO     | USIM1 reset                  | P1                                           | -                                                                                  |  |

| USIM1_DATA           | 45        | В      | USIM1 data input and output  | P1                                           | Pulling up this pin to USIM1_VCC via a 4.7 k $\Omega$ resistor is required.        |  |

| USIM1_CLK      | 46 | DO  | USIM1 clock output             | P1                                                              | -                                                                                                                                              |  |

|----------------|----|-----|--------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| USIM2_DET*     | 83 | DI  | USIM2 hot-swapping detection   | P3                                                              |                                                                                                                                                |  |

| USIM2_CLK*     | 84 | DO  | USIM2 clock output             | P1                                                              | Currently not supported.                                                                                                                       |  |

| USIM2_RESET*   | 85 | DO  | USIM2 reset                    | P1                                                              |                                                                                                                                                |  |

| USIM2_DATA*    | 86 | В   | USIM2 data input and output    | P1                                                              | - Canonaly net cappendar                                                                                                                       |  |

| USIM2_VCC*     | 87 | PO  | USIM2 power output             | JSIM2 power output Either 1.8 V or 3.0 V USIM card is supported |                                                                                                                                                |  |

| USB interfaces |    |     |                                |                                                                 |                                                                                                                                                |  |

| USB_VBUS       | 8  | Al  | Voltage detection              | 3.5 V - 5.25 V, typical value: 5.0V                             | -                                                                                                                                              |  |

| USB_DP         | 9  | AIO | USB data +                     |                                                                 | USB 2.0. This pin is used for software                                                                                                         |  |

| USB_DM         | 10 | AIO | USB data -                     | <del>)</del>                                                    | download and data transmission. Route the DM and DP traces as differential pairs, and the impedance of the differential pairs is $90~\Omega$ . |  |

| I2C interface  |    |     |                                |                                                                 |                                                                                                                                                |  |

| I2C_SCL        | 40 | DO  | I2C clock                      | P3                                                              | Connecting this pin through a pull-up                                                                                                          |  |

| I2C_SDA        | 41 | В   | I2C data                       | P3                                                              | resistor (4.7 k $\Omega$ recommended) to VDD_1P8 is required.                                                                                  |  |

| PCM interface  |    |     |                                |                                                                 |                                                                                                                                                |  |

| PCM_CLK        | 4  | DO  | PCM data clock                 | P3                                                              | Leave this pin open if unused.                                                                                                                 |  |

| PCM_SYNC       | 5  | DO  | PCM data frame synchronization | P3                                                              | Leave this pin open if unused.                                                                                                                 |  |

| PCM_DIN        | 6  | DI  | PCM data input                 | P3                                                              | Leave this pin open if unused.                                                                                                                 |  |

| PCM_DOUT           | 7                                                                                                                | DO  | PCM data output                | P3 | Leave this pin open if unused.                                                                                                                                                                                    |

|--------------------|------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog audio inte  | erface                                                                                                           |     |                                |    |                                                                                                                                                                                                                   |

| SPK_P              | 121                                                                                                              | AO  | Analog audio output +          | -  | Supports driving power of up to 37 mW                                                                                                                                                                             |

| SPK_N              | 122                                                                                                              | АО  | Analog audio output -          | -  | with a 32 $\Omega$ load. If higher driving power is required, connect this interface to an external power amplifier.                                                                                              |

| MIC_BIAS           | 120                                                                                                              | РО  | Microphone bias voltage output | -  | -                                                                                                                                                                                                                 |

| MIC_N              | 119                                                                                                              | Al  | MIC analog input -             | -  | <del>-</del>                                                                                                                                                                                                      |

| MIC_P              | 126                                                                                                              | Al  | MIC analog input +             | -  | -                                                                                                                                                                                                                 |

| Antenna interface  | •                                                                                                                |     |                                |    |                                                                                                                                                                                                                   |

| ANT_MAIN           | 60                                                                                                               | AIO | Main antenna                   | /  | Control the impedance of antenna traces at 50 $\Omega$ .                                                                                                                                                          |

| Other functional i | nterfaces                                                                                                        |     |                                |    |                                                                                                                                                                                                                   |

| USB_BOOT           | 75                                                                                                               | DI  | Emergency download control     | P3 | Active high. Pulling this pin high to VDD_1P8 can set the module into USB emergency download mode.                                                                                                                |

| RF_DISABLE*        | 18                                                                                                               | DI  | Flight mode control            | P3 | -                                                                                                                                                                                                                 |

| AP_READY*          | 19                                                                                                               | DI  | Application processor ready    | P3 | -                                                                                                                                                                                                                 |

| RESERVED           | 2, 11 - 14, 16, 24 -<br>28, 49, 51, 56 - 57,<br>63 -66, 76 - 78, 88,<br>92 -95, 97 - 99, 103 -<br>118, 123 - 125 |     | Reserved pin                   | -  | It is reserved for future function expansion or functions not open to the user. There may be more than one pin named RESERVED, which may have different functions or definitions. Leave these RESERVED pins open. |

# 4 Application Interfaces

N717-EA provides interfaces for control, communications, peripherals RF and other functions to meet the requirements of different product application scenarios.

This chapter describes how to design each interface and provides reference designs and guidelines.

## 4.1 Power Interfaces

The schematic design and PCB layout of the power supply part are the most critical process in application design and they will determine the performance of the actual applications. Please read the design guidelines of power supply and comply with the correct design principles to obtain the optimal circuit performance.

| Signal  | Pin SN | Pin SN I/O Function description Remarks |                                                     |                                                                                                                                  |

|---------|--------|-----------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| VBAT_BB | 32, 33 | PI                                      | Module baseband supply input                        | The external power supply must ensure at least 0.8 A current for VBAT_BB.                                                        |

| VBAT_RF | 52, 53 | PI                                      | RF supply input                                     | The external power supply must ensure at least 2.2 A current for VBAT_RF.                                                        |

| VDD_1P8 | 29     | РО                                      | 1.8 V power output                                  | With output currents of up to 50 mA, used only for voltage-level translation. It is recommended to add ESD protection when used. |

| GND     |        |                                         | 50, 54 - 55, 58 - 59, 61-<br>82, 89 - 91, 100 - 102 | Make sure all GND pins are grounded.                                                                                             |

#### 4.1.1 VBAT

The design of power supply includes two parts: schematic design and PCB layout.

## Power Supply Design

In GSM/GPRS mode, RF data transmission is intermittent, the frequency of burst transmission is about 217 Hz and the peak current is up to 3 A. Therefore, it is necessary to ensure the following conditions: The driving capacity of the power supply is sufficient, the power supply trace is wide enough to reduce the impedance, and a large capacitance is provided to improve the freewheeling current, thereby ensuring that the voltage will not drop below the minimum operating voltage of the module at the instantaneous peak current.

0.577ms ≤ T ≤ 2.038ms

Burst

Drop

VBAT

Whin: 3.3V ------

Figure 4-1 Voltage drops of the power supply.

Never use a diode to make the voltage drop between a higher input and the module power supply. The forward voltage drop  $V_f$  of diode has two characteristics: one is that it increases with the increase of the forward current, the other is that it increases significantly at a low temperature. Note that, if there is an instantaneous high current, the above characteristics will lead to unstable operating voltage of the module, and even damage the module.

The power supply design of the N717-EA module depends on the input voltage of power supply. There are three power input types:

- 3.4 V 4.2 V power input (typical value: 3.6 V, provided by a battery)

- 4.2 V 5.5 V power input (typical value: 5.0 V, provided by a computer internal rectifier)

- 5.5 V 24 V power input (typical value: 12 V, provided by a DC-DC power supply solution)

The design recommendations for 3.4 V - 4.2 V power input are as follows:

VBAT\_RF Test point VBAT\_BB Power Supply I max N717-EA Module C1 С3 C4\_ C5 C6 C7 D1 **100uF**10uF 100nF 33pF Close to the pin of the module Close to the pin of the module

Figure 4-2 Recommended power supply design 1

- The maximum input voltage of the module power supply is 4.2 V, and the typical value is 3.6 V.

- In order to get a stable power source, it is recommended to use a TVS diode with suggested low reverse voltage (VRWM 4.5 V) and peak power (Ppp = 2800 W (tp = 8/20 us)) at D1. Keep the placement of the TVS diode close to the power input interface to ensure that the power surge voltage is clamped before entering the back-end circuit, thus protecting the back-end components and the module.

- To decrease voltage drops during bursts, a large bypass tantalum capacitor (220 μF or 100 μF) or aluminum capacitor (470 μF or 1000 μF) is expected at C1 and C6. Their maximum safe operating voltage should be larger than 2 times the voltage of the power supply.

- Keep the low ESR bypass capacitors (C2, C3, C4, C5) as close to the module as possible to filter out high-frequency interference in the power supply.

If it is necessary to control the power supply, the following circuit design is recommended:

Q1 VIN **VBAT** C1 R4: 22uF | 0.1uF 100kΩ C5 C3 100uF 10uFT 0.1uF 1100pF R5 10kΩ PWR\_EN 4.7kΩ Q2 R2 47kO

Figure 4-3 Recommended power supply design 2

- Select an enhanced P-MOSFET at Q1, of which the withstand voltage is high ( $V_{dss} = -12 \text{ V}$ ), drain current is high ( $I_{D(MAX)} = -3.5 \text{ A}$ ) and RDS is low ( $R_{ds(on)} = 108 \text{ m}\Omega$ ).

- Select a common NPN transistor at Q2. Reserve enough tolerances of R1 and R2 in design, especially for the situation in which the break-over voltage on the base of the transistor increases at a low temperature; it is recommended that the value of R2 be at least 10 times that of R1.

- Keep the placement of C3 close to the module. Select a large-capacity tantalum electrolytic capacitor (220 μF or 100 μF) or aluminum electrolytic capacitor (470 μF or 1000 μF) at C3 to improve the instantaneous large freewheeling current of the power supply, and its withstand voltage value should be larger than 2 times the power supply voltage.

- Keep the low ESR bypass capacitors (C4, C5, C6, C7) as close to the module as possible to filter out high-frequency interference in the power supply.

The design recommendations for the 4.2 V - 5.5 V power input are as follows:

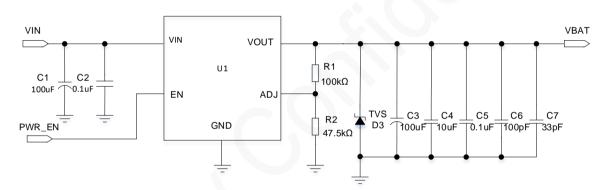

Figure 4-4 Recommended power supply design3

- If the power input voltage at VIN is similar to the VBAT voltage, it is recommended to use an LDO while supplying power for the module, which is simple with high efficiency.

- Select an LDO with a maximum output current of no greater than 3 A at U1 to ensure the normal performance of the module.

- Keep the placement of the TVS diode close to the power input interface to ensure that the power surge voltage is clamped before entering the back-end circuit, thus protecting the back-end components and modules.

- Keep the placement of C3 close to the module. Select a large-capacity tantalum electrolytic capacitor (220 μF or 100 μF) or aluminum electrolytic capacitor (470 μF or 1000 μF) at C3 to improve the instantaneous large freewheeling current of the power supply, and its withstand voltage value should be larger than 2 times the power supply voltage.

- Keep the low ESR bypass capacitors (C4, C5, C6, C7) as close to the module as possible to filter out high-frequency interference in the power supply.

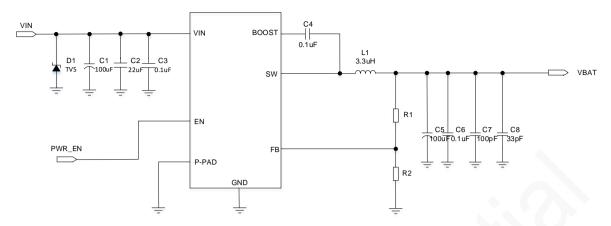

The design recommendations for the 5.5 V - 24 V power input are as follows:

Figure 4-5 Recommended power supply design4

- If there is a high voltage drop between the power input and VBAT, a DC-DC design should be selected for higher efficiency, and the output current should be at least 3 A.

- Keep the TVS diode (D1) close to the power input interface to ensure that the power surge voltage is clamped before entering the back-end circuit, thus protecting the back-end components and modules.

- Keep the placement of C5 close to the module. Select a large-capacity aluminum electrolytic capacitor (220 μF or 100 μF) or tantalum electrolytic capacitor (470 μF or 1000 μF) at C5 to improve the instantaneous large freewheeling current of the power supply, and its withstand voltage value should be more than 2 times the power supply voltage.

- Keep the low ESR bypass capacitors (C6, C7, C8) as close to the module as possible to filter out high-frequency interference in the power supply.

When the module encounters a running exception and cannot be switched off in a normal method, it is recommended to disconnect the power of the module and then power and turn it on to restore the module.

#### **PCB** Layout

Place an ESR capacitor at the output of the power source to suppress peak current. In order to protect the back-end components, it is necessary to add a TVS diodes at the input of the power supply to suppress voltage spikes. The circuit design is important, and the component placement and PCB routing are equally important. Several key points in power supply design are as follows:

• The TVS diode can absorb instantaneous high-power pulse and can withstand instantaneous pulse current peaks up to tens or even hundreds of amperes, with extremely short response time of voltage clamping. Keep the TVS diode as close to the power input as possible, ensuring that the surge voltage can be clamped before the pulse is coupled to the adjacent PCB traces.

- Place the bypass capacitor as close as possible to the power supply pin of the module to filter out high-frequency noise signals in the power supply.

- For the main power circuit of the module, ensure that the PCB trace is wide enough that 3 A current can be safely passed, with no significant loop voltage drop. Keep the VBAT\_BB trace width be at least 0.8 mm and the VBAT\_RF trace width be at least 2.2 mm and ensure that the ground plane of the power supply part is as complete as possible. In addition, try to make power traces short and wide.

- Keep noise-sensitive circuits, such as audio circuits and RF circuits far away from the power circuitry, especially when the DC-DC power supply is used.

- The voltage frequency of the SW pin of the DC-DC power supply is high, so the loop area should be minimized. Keep sensitive components far away from the SW pin of the DC-DC component to prevent noise coupling. Place feedback components as close as possible to the FB pin.

- The thermal-dissipation pads and GND pins of the DC-DC chip should be grounded to ensure good thermal dissipation and noise signal isolation.

## 4.1.2 VDD 1P8

VDD\_1P8 power is normally on and cannot be turned off even in sleep mode. If an external circuit is connected, the sleep power consumption will increase. It is recommended that VDD\_1P8 is used only for voltage-level translation, not for other purpose, and ESD protection is required when using VDD\_1P8.

N717-EA provides one VDD 1P8 interface with a 1.8 V voltage and output currents up to mA.

## 4.2 Control Interfaces

| Signal   | Pin SN | I/O | Function description  | Remarks    |

|----------|--------|-----|-----------------------|------------|

| PWRKEY_N | 15     | DI  | Module on/off control | Active low |

| RESET_N  | 17     | DI  | Module reset input    | Active low |

## 4.2.1 Module Power-on

Table 4-1 Power-on description

| Power-on<br>trigger<br>method                  | Supported or not | Power-off method                                                                  | Notice                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------|------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Key                                            | Supported        | Press the power-on key for no less than 2s and then release it.                   | When the module is in power-on mode, do not disconnect the power supply directly;                                                                                                                                                                                                                                                                       |

| Pulse                                          | Supported        | Inputting a low level at PWRKEY_N for no less than 2s.                            | otherwise, the flash inside the module will be damaged.                                                                                                                                                                                                                                                                                                 |

| Auto power-<br>on<br>(PWRKEY_N<br>be grounded) | Supported        | Send the power-off AT command to the module and then disconnect its power source. | When you need to design an auto power-on circuit for the module by referring to Figure 4-9, and repeated power-on/off operations are required, you should to add a module reset solution using the RESET_N pin by referring to Figure 4-12, since powering off the module while it is using the auto power-on solution may result in a startup failure. |

## Power-on via PWRKEY\_N

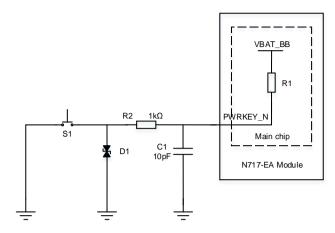

The following describes two reference design circuits for module power-on.

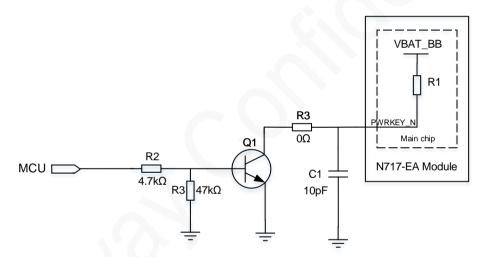

Figure 4-6 shows the reference design of key-control startup.

Figure 4-6 Reference design of key-control startup

Figure 4-7 shows the reference design of MCU-control startup.

Figure 4-7 Reference design of MCU-control startup

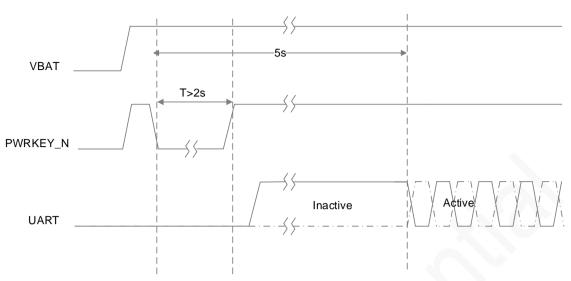

#### Power-on process

After the VBAT input is powered, to switch the module on, the PWRKEY\_N interface must be asserted low for 3s and then released. The AT function is available 5 seconds after the assertion of PWRKEY\_N.

After turning on the module, it is not yet activated because the SW initialization process of the module is still in process internally. It takes some time to fully complete the HW and SW initialization of the module. During the Initialization state, AT commands are not available. Please access the module after the Initialization state completes. The module startup process is shown in the following figure.

Figure 4-8 Power-on process

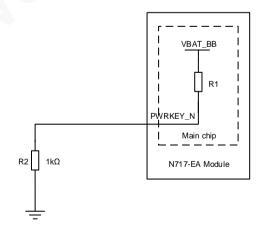

#### Auto Power-on

- When you need to design an auto power-on circuit for the module and do not require a power-off function, you should connect the PWRKEY N pin through a pull-down resistor ( $1k\Omega$  recommended) to ground.

- Note that adding a reset solution during designing the auto power-on circuit is a must when the module requires to be repeatedly turned on and off. To ensure a proper power-on/off operation, reset the module at least one time after power-on. For the reset circuit, see Figure 4-12.

Figure 4-9 Reference design of automatic startup once powered up

## 4.2.2 Module Power-off

- When the module is in power-on mode, do not disconnect the power supply directly; otherwise, the flash

inside the module will be damaged. Do not directly disconnect the power of the module in power-on mode,

if there is not any abnormality.

- When you are using the AT command to switch off the module, ensure that PWRKEY\_N will at a highlevel voltage all the time. Otherwise, the module will start up automatically after the AT command execution.

Two methods are available to switch off the module: hardware shutdown and software shutdown

- Hardware power-off via PWRKEY N

- Software power-off via AT command

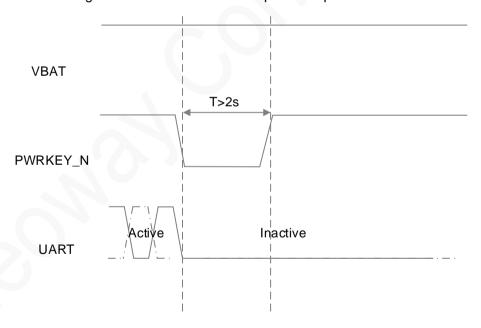

#### Hardware Power-off via PWRKEY\_N

When the module is in power-on mode, to turn off the module, the PWRKEY\_N pin must be asserted low for greater than 2s and then released.

The following figure shows the hardware power-off process:

Figure 4-10 N717-EA hardware power-off process

#### Software Power-off via AT Command

When the module is in power-on mode, to turn off the module, send it the power-off AT command. For details of the AT command, see *Neoway\_N717\_AT\_Commands\_Manual*.

## 4.2.3 Module Reset

If the module encounters abnormalities such as system crash, you can reset the module system using the RESET\_N pin to restore it. Therefore, it is strongly recommended to add a reset solution using the RESET\_N pin when designing your PCB by referring to Figure 4-11 or Figure 4-12.

When the module is in power-on mode, inputting a low voltage at RESET\_N for more than 50 ms can reset the module. For the module reset process, see Figure 4-13.

The following describes two reference design circuits for module reset.

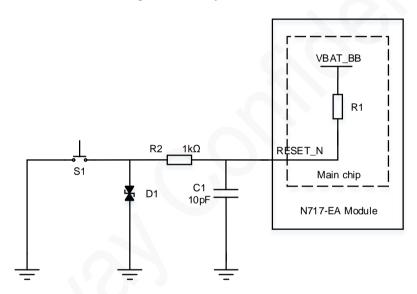

#### Key-control reset

Figure 4-11 Key-control reset

#### MCU-control reset

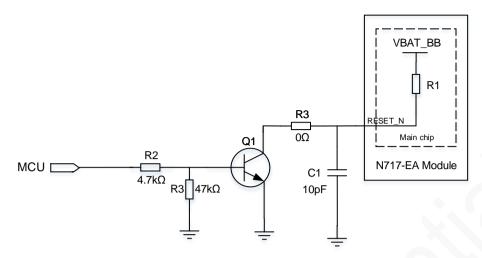

If you use a 1.8 V / 2.8 V / 3.3 V MCU system, it is recommended to add a triode to for isolation. Refer to the following figure for specific design.

Figure 4-12 MCU-control reset

N717-EA module reset process is shown in the following figure.

VBAT

RESET\_N

T>50ms

UART

Active Inactive

Figure 4-13 Module reset process

## 4.3 Peripheral Interfaces

N717-EA provides a variety of peripheral interfaces.

In all reference designs in this section, the I/O direction indicated by the module peripheral interface pin name is based on the module, while the peripheral pin naming is based on the peripheral component itself. For example, UART\_TXD of the module indicates the pin of the module for sending data, and MCU RXD indicates the pin for MCU receiving data, so two pins should be connected.

In the process of peripheral model selection and design, please check the pin naming is based on the

module or peripheral.

#### 4.3.1 USB

| Signal   | Pin SN | I/O | Function description | Remarks                                                                                                                                                 |

|----------|--------|-----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_VBUS | 8      | Al  | Voltage detection    | 3.5 V < USB_VBUS < 5.25 V, typical value: 5 V.                                                                                                          |

| USB_DP   | 9      | AIO | USB data +           | USB 2.0. This pin is used for                                                                                                                           |

| USB_DM   | 10     | AIO | USB data -           | software download and data transmission. Route the DM and DP traces as differential pairs, and the impedance of the differential pairs is $90 \Omega$ . |

N717-EA can implement program download, data communications, and debugging through the USB interface. Only slave mode is supported for USB of the module, which can be used as required. The recommended USB connection circuit is shown in Figure 4-14.

Figure 4-14 Recommended design of the USB interface

#### Schematic Design Guidelines

- Connect a 1 μF (C1) and a 33 pF (C2) filter capacitors as well as an ESD component (D1) in parallel to the USB\_VBUS trace.

- Ensure that the junction capacitance of the ESD components (D2 and D3) in parallel to the USB DP and USB DM traces be smaller than 0.5 pF.

- Connecting a resistor of less than 10 Ω in series between the USB\_DM and USB\_DP pins of the module and the USB\_DP and USB\_DM pins of the USB host can effectively improve the EMI performance of the USB.

#### PCB Design Guidelines

- Place the filter capacitor on the USB\_VBUS as close to the module pins as possible, and place the ESD component as close to the USB connector as possible.

- Place the paralleled ESD component of the USB\_DP and USB\_DM traces as close to the USB connector as possible.

- It is important to route USB signal traces as differential pairs with ground surrounded. The impedance of the USB differential traces should be 90 Ω. The traces from the USB interface of your application PCB to the module must be isolated from other signal traces.

#### 4.3.2 UART

| Signal         | Pin SN | I/O | Function description | Remarks                                |

|----------------|--------|-----|----------------------|----------------------------------------|

| UART_DTR       | 30     | DI  | Data terminal ready  |                                        |

| UART_RXD       | 34     | DI  | UART data input      | Software version                       |

| UART_TXD       | 35     | DO  | UART data output     | (Standard): For communication based on |

| UART_RTS       | 36     | DO  | UART ready to send   | AT commands.                           |

| UART_CTS       | 37     | DI  | UART clear to send   | Software version (Open):               |

| UART_DCD       | 38     | DO  | Data carrier detect  | For data transmission.                 |

| UART_RI        | 39     | DO  | Ring indication      | _                                      |

| DEBUG_UART_RXD | 22     | DI  | DEBUG data input     | For module debugging                   |

| DEBUG_UART_TXD | 23     | DO  | DEBUG data output    | only.                                  |

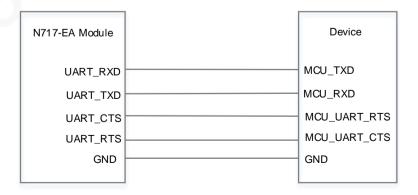

N717-EA provides two UART interfaces, one of which supports hardware flow control. The UART interface supports a 1.8 V voltage and its default buad rate is 115200 bps. The following figure shows recommended design of the interface.

Figure 4-15 Reference design of the UART interface

#### Schematic Design Guidelines

- Pay attention to the correspondence between signal flow direction and connection.

- It is prohibited to use diodes for voltage-level translation.

If the the logic voltage of UART does not match that of the MCU, add a voltage-level translation circuit outside the module. Three voltage-level translation circuits are recommended based on the differences in logic levels and rates.

The actual parameter values of the components used in the voltage-level translation circuit should be adjusted according to the actual test results. Note the differences between different circuit voltage-level translation solutions.

Voltage-level translation chip circuit

If the UART baud rate is greater than 115200 bps, it is recommended to design the voltage-level translation solution by referring to the recommended voltage-level translation circuit 1. As shown in Figure 4-16.

VDD\_1P8 □ VCC IO VCC VL UART TXD <sup>[</sup> IO\_VL1 IO\_VCC1 MCU\_RXD UART RXD ≤ IO\_VCC2 IO\_VL2 MCU\_TXD VDD\_1P8 ΕN **GND** C2 0.1uF

Figure 4-16 Recommended voltage-level translation circuit 1

- VL is the reference voltage for IO\_VL1 and IO\_VL2, and the voltage range is 1.5 V 5.5 V.

- VCC is the reference voltage for IO\_VCC1 and IO\_VCC2, and the voltage range is 1.5 V 5.5 V.

- EN is an enable pin, which works at a voltage of greater than VL-0.2 V. In the above circuit,

the EN pin is directly connected to VDD 1P8 and the level translator chip is always working.

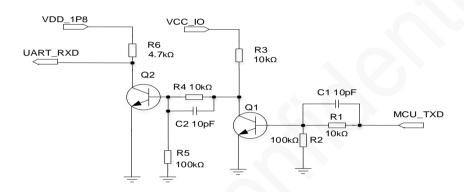

- Dual-triode voltage-level translation circuit

If the UART baud rate is not greater than 115200 bps, it is recommended to design the voltage-level translation solution by referring to the recommended voltage-level translation circuit 2.

VDD\_1P8 VCC\_IO

VDD\_1P8 VCC\_IO

R6

4.7kΩ MCU\_RXD

Q2

R4 10kΩ

Q2

R4 10kΩ

R2

Q2

R5

100kΩ

Figure 4-17 Recommended voltage-level translation circuit 2

MCU\_TXD and MCU\_RXD are the sending and receiving ports of MCU respectively, and UART\_TXD and UART\_RXD are the sending and receiving ports of module respectively. VCC\_IO is the IO voltage of MCU and VDD\_1P8 is the IO voltage of the module.

The circuit translates the voltage level through the turn-on and turn-off of the triode, and the dual triode can achieve higher voltage difference after voltage-level translation.

#### Schematic Design Guidelines

- Ensure that the base voltage of the triode is operating within the temperature range and the transistor can be fully turned on.

- It is recommended to reserve the acceleration capacitor, which can adjust the delay of the voltage-level translation circuit in some cases.

- Single-triode voltage-level translation circuit

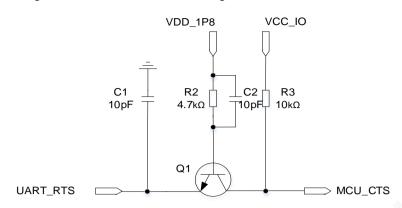

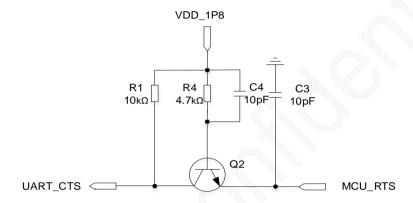

For the CTS/RTS/DCD/RI pin, it is recommended to design the voltage-level translation solution by referring to Figure 4-18.

Figure 4-18 Recommended voltage-level translation circuit 3

MCU\_CTS and MCU\_RTS are the MCU-side signals, while UART\_CTS and UART\_RTS are the module-side signals. VCC\_IO is the IO voltage of MCU and VDD\_1P8 is the IO voltage of the module.

This single-triode voltage-level translation circuit is a one-way translation solution that works by conduction and cutoff of the triode. Please note the signal flow direction.

#### Schematic Design Guidelines

- The voltage difference between the high level and low level does not exceed 2 V.

- It is recommended to reserve the speed-up capacitor and adjust its capacitance value according to actual test results.

- The transistor base voltage is the lower value of the level between both sides.

### 4.3.3 USIM

| Signal    | Pin SN | I/O | Function description         | Remarks |

|-----------|--------|-----|------------------------------|---------|

| USIM1_DET | 42     | DI  | USIM1 hot-swapping detection | -       |

| USIM1_VCC | 43     | РО  | USIM1 power output           | -       |

| USIM1_RESET | 44 | DO | USIM1 reset                  | -                                                                |

|-------------|----|----|------------------------------|------------------------------------------------------------------|

| USIM1_DATA  | 45 | В  | USIM1 data input and output  | This pin is pulled up to USIM1_VCC via a 4.7 $k\Omega$ resistor. |

| USIM1_CLK   | 46 | DO | USIM1 clock output           | -                                                                |

| USIM2_DET   | 83 | DI | USIM2 hot-swapping detection |                                                                  |

| USIM2_CLK   | 84 | DO | USIM2 clock output           |                                                                  |

| USIM2_RESET | 85 | DO | USIM2 reset                  | Currently not supported.                                         |

| USIM2_DATA  | 86 | В  | USIM2 data input and output  |                                                                  |

| USIM2_VCC   | 87 | РО | USIM2 power output           |                                                                  |

|             |    |    |                              |                                                                  |

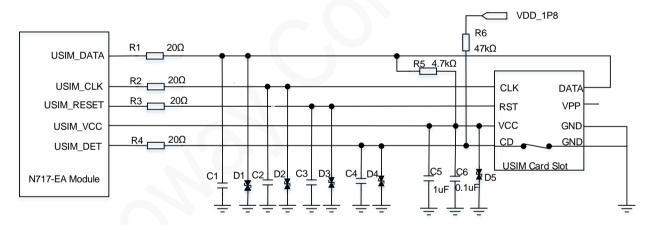

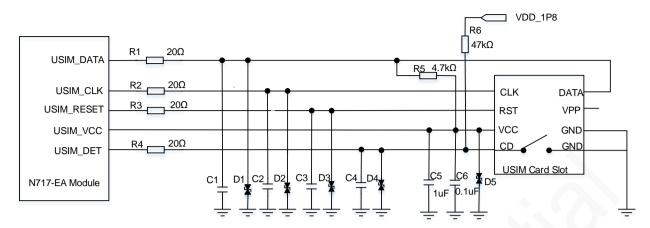

N717-EA provides two USIM interfaces that supports either 1.8 V or 3.0 V USIM card. USIM1 is valid by default. The recommended design of the USIM interface is shown in Figure 4-19 and Figure 4-20.

Figure 4-19 Recommended design of the USIM interface (normally close connector)

Figure 4-20 Recommended design of the USIM interface (normally open connector)

#### Schematic Design Guidelines

- USIM\_VCC is the power supply of the USIM card, with load capacity of up to 50 mA. It is only

used as power supply for the USIM card and shall not supply power to other loads.

- The USIM\_DATA pin is not pulled up internally, so connecting it through a 4.7 kΩ external pull-up resistor to USIM\_VCC is required.

- USIM\_CLK is the clock signal pin for USIM card. The applications in complex electromagnetic

environment require ESD protection of high quality, so it is recommended to add ESD protection

components (junction capacitance no more than 7 pF) on each signal traces or directly add an

integrated ESD device for alternative.

- Add a series resistor of no more than 20 Ω between each of the USIM\_DATA, USIM\_RESET, USIM\_CLK, and USIM\_DET pin and the card connector to enhance ESD performance. The resistors should be placed close to the card connector.

- C1 C4 are in parallel to each USIM signal trace and are used to attach high-frequency filter capacitors. Their capacitance value should be not more than 10 pF.

- N717-EA supports USIM card detection, and USIM\_DET is a 1.8 V interrupt pin. The USIM

detection circuit works by checking the level of the voltage across the USIM\_DET pin before and

after a USIM card is inserted.

- For the reference design circuit in Figure 4-19, SIM\_DET is grounded before a USIM card is inserted and is pulled up to a 1.8 V voltage after a USIM card is inserted, so the high voltage level means USIM card detected while the low voltage level means no USIM card detected.

- For the reference design circuit in Figure 4-20, SIM\_DET is in a 1.8 V voltage before a

USIM card is inserted and is grounded after a USIM card is inserted, so the high voltage

level means no USIM card detected while the low voltage level means USIM card detected.

If the USIM hot-swapping function is not required, the USIM\_DET pin must be pulled up to 1.8 V via a 47 k $\Omega$  resistor in series, and the USIM hot-swapping detection function must be disabled in the software. Figure 4-21 shows the reference design of the USIM card interface (without hot-swapping function) .

USIM\_DATA R<u>5 4</u>.7kΩ 20Ω USIM\_CLK CLK DATA USIM\_RESET RST VPP USIM\_VCC VCC **GND** USIM\_DET R4 D1 C2 D2 R6 <u>C</u>5 N717-EA Module ∐47kΩ 0.1uF 1uF □ VDD\_1P8

Figure 4-21 Reference design of USIM card interface (without hot swap function)

#### PCB Design Guidelines

- USIM cards and their signal traces often be jammed by RF radiation, resulting in USIM abnormalities. Therefore, keep the USIM card connector far away from the antenna and RF circuits.

- Keep the USIM card connector close to the module and keep USIM traces as short as possible.

- On the USIM traces, connect the series resistors and ESD protection components close to the USIM card connector.

- To avoid cross-talk between USIM signal traces, shield them with surrounded ground.

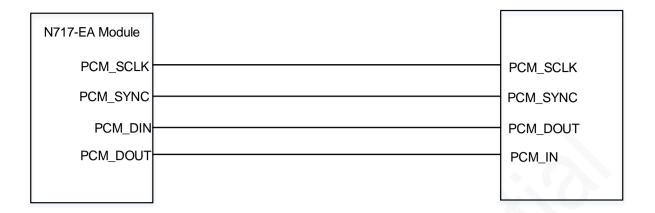

### 4.3.4 PCM

| Signal   | Pin SN | I/O | Function description           | Remarks |

|----------|--------|-----|--------------------------------|---------|

| PCM_CLK  | 4      | DO  | PCM data clock                 | -       |

| PCM_SYNC | 5      | DO  | PCM data frame synchronization | -       |

| PCM_DIN  | 6      | DI  | PCM data input                 | -       |

| PCM_DOUT | 7      | DO  | PCM data output                | -       |

N717-EA provides one PCM interface, supporting a 1.8 V voltage. The following shows the reference design of the PCM interface.

Figure 4-22 Reference design of the PCM interface

### Schematic Design Guidelines

If the logic levels between the N717-EA module and Codec do not match, you should add a voltage-level translation solution.

#### PCB Design Guidelines

- Avoid crossing of PCM signal traces with other traces. If the crossings are unavoidable, 90° crossings should be used to minimize coupling of the traces.

- Route PCM traces as far away as possible from areas that may introduce ESD.

- Shield the PCM\_SCLK trace with surrounded ground, and for other PCM traces, shielding with surrounded ground is also recommended.

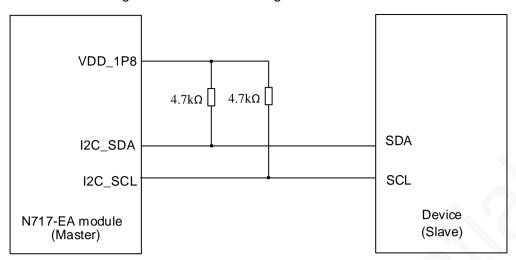

### 4.3.5 I2C

| Signal  | Pin SN | I/O | Function description | Remarks                                               |

|---------|--------|-----|----------------------|-------------------------------------------------------|

| I2C_SCL | 40     | DO  | I2C clock            | Connecting this pin through a pull-up                 |

| I2C_SDA | 41     | В   | I2C data             | resistor (4.7 kΩ recommended) to VDD_1P8 is required. |

N717-EA provides one 1.8 V I2C interface, supporting only master mode and speed rates up to 3.4 Mbps. The following figure shows the recommended reference design of the interface.

Figure 4-23 Reference design of the I2C interface

## 4.4 Audio Interfaces

N717-EA provides many audio input and output interfaces to meet the needs of audio in different environments.

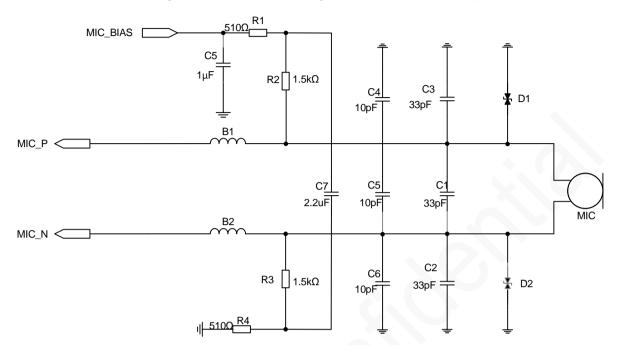

## 4.4.1 Analog Audio Input

| Signal   | Pin SN | I/O | Function description           | Remarks |

|----------|--------|-----|--------------------------------|---------|

| MIC_BIAS | 120    | РО  | Microphone bias voltage output | -       |

| MIC_N    | 119    | Al  | MIC analog input -             | -       |

| MIC_P    | 126    | Al  | MIC analog input +             | -       |

N717-EA supports one MIC differential input. The following figure shows the reference design.

Figure 4-24 Reference design of the differential MIC input

#### Schematic Design Guidelines

- D1 and D2 are designed to attach TVS diodes, which are used to prevent MIC from introducing ESD and damaging the module.

- C1 and C6 are designed to attach filter capacitors, which are mainly used to filter out interference signals and their capacitance values can be adjusted according to actual debugging result.

- B1 and B2 are designed to attach magnetic beads, which are used to filter out high-frequency noise. Magnetic beads with 1800  $\Omega$  @ 100 MHz or higher and DC impedance less than 1.5  $\Omega$  are preferred. It is recommended to use dedicated magnetic beads for audio.

- It is recommended to use an electret microphone with built-in RF filter dual capacitors (such as 10 pF and 33 pF) to filter RF interference from the source and reduce TDD coupling noise.

#### PCB Design Guidelines

- MIC P and MIC N traces should comply with the differential rules.

- Shield the audio traces with surrounded ground. Keep them not less than 3 times the audio trace width away from other signal traces.

- Place RF filter capacitors close to the audio components or pins.

- Keep the audio traces far away from interference sources, such as DC-DC power supply.

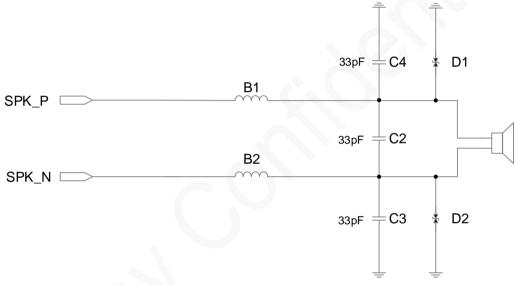

## 4.4.2 Analog Audio Output

| Signal | Pin SN | I/O | Function description  | Remarks                                                                                      |  |

|--------|--------|-----|-----------------------|----------------------------------------------------------------------------------------------|--|

| SPK_P  | 121    | АО  | Analog audio output + | Supports driving power of up to 37 mW with a 32 Ω load. If higher driving power is required, |  |

| SPK_N  | 122    | АО  | Analog audio output - | connect this interface to an external powe amplifier.                                        |  |

The following shows the reference design of the audio output interface.

Figure 4-25 Reference design of the differential SPK input

#### Schematic Design Guidelines

- C2, C3 and C4 are designed to attach filter capacitors, which are used to filter out highfrequency interference.

- D1 and D2 are designed to attach TVS diodes, which are used to prevent ESD from damaging the module.

- B1 and B2 are designed to attach magnetic beads, which are used to filter out high-frequency noise. It is recommended to use dedicated magnetic beads for audio frequency.

- Special attention should be paid to the DC resistance of the magnetic bead. The impedance of the audio output device is generally small, so if the DC resistance of magnetic bead is too large, too much audio power will be consumed. In principle, the smaller DC resistance of the magnetic bead is preferred. It is recommended to select the magnetic bead with DC resistance less than 0.1 Ω.

PCB Design Guidelines

- The audio signal traces should be wide enough (0.5 mm is recommended) to bear large current when audios are outputted at a highest volume. Isolate the audio traces from high-speed digital signals and clocks as well as other analog signal traces. No signal trace crossing is allowed. Reserve enough ground via-holes and ground reference layer protection.

- Keep the audio traces far away from antenna to reduce jamming. Avoid parallel layout between power supply traces and the audio traces.

- It is important to route the audio signal traces as differential pairs.

## 4.5 RF Interface

| Signal   | Pin SN | I/O | Function description | Remarks |

|----------|--------|-----|----------------------|---------|